场效应晶体管(FET)是半导体芯片的核心部件,其尺寸大小决定了芯片的集成密度。而FET晶体管的终极物理尺寸,很大程度上取决于在栅极处Si/SiO2界面的结构和性能:界面的尺寸过大会导致集成度降低,芯片性能下降;界面的尺寸小,晶体管中源极到漏极之间的电流会受到量子隧穿效应的影响,导致明显的漏电和高的能耗。当前芯片中晶体管的栅极长度(即源极到漏极间的距离)实际上已经达到了几纳米的尺寸,如台积电最新的5nm工艺以及intel最新的10nm工艺,正逐渐逼近硅材料的物理极限,量子隧穿效应导致的漏电已经成为现实工艺困境。因此如何在现代晶体管的设计中充分考虑量子效应影响,在开路电流和闭路漏电之间取得最优的平衡,是关键的科学问题,需要对Si/SiO2界面结构和量子隧穿性能达到新的认知高度。

然而,目前的理论和实验方法很难获知精确的Si/SiO2界面原子级别结构。对于实验,界面结构隐藏在材料内部,传统实验方法,比如透射电子显微镜(TEM)很难直接观察。而对于理论计算,界面结构预测缺乏完备和快速的方法,无法考虑各种可能的界面取向,无法精确快速描述界面处的成断键相互作用。

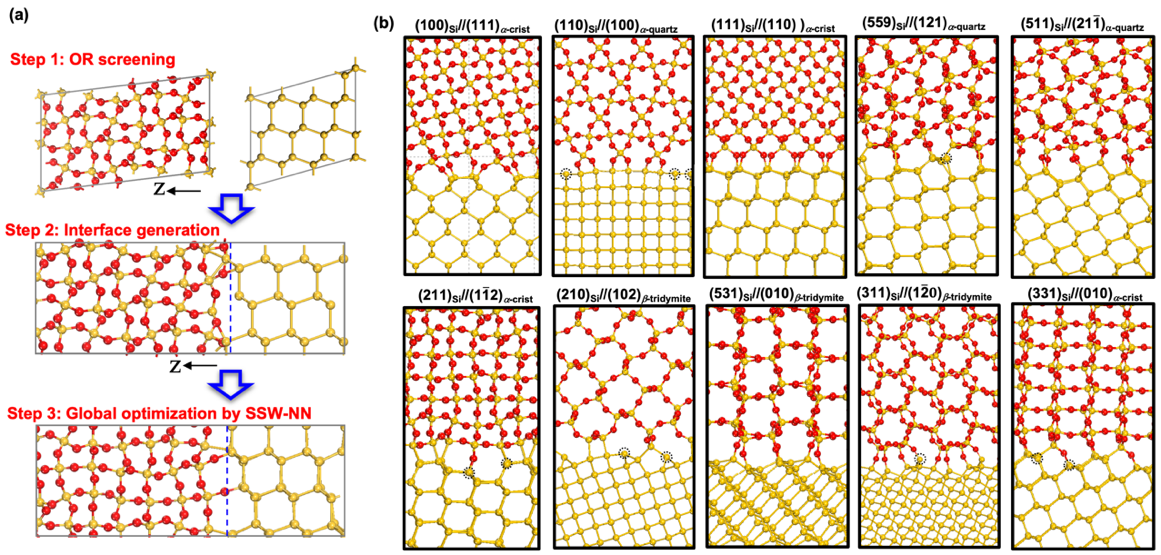

近期,复旦大学李晔飞和刘智攀提出了一种基于机器学习计算的界面结构预测方法(ML-interface),解决了不同晶体间界面结构预测的难题。该方法基于唯象理论、图论、全局势能面搜索和机器学习势函数等理论计算方法,仅需不同材料体相晶胞的晶体结构作为输入参数,即能可靠预测任意可能界面的原子结构。具体来说,该方法首先采用马氏体晶体学唯象理论(PTMC)筛选出两种晶体相间所有晶格匹配的界面取向关系。然后,通过图论方法产生合理的界面原子模型。最后,采用基于机器学习势函数的全局势能面搜索方法(SSW-NN)确定最稳定的界面结构(图1A)。采用该方法,李晔飞和刘智攀从数千个候选结构对象中解析出了所有稳定 Si/SiO2界面结构。相关研究成果以《基于机器学习的全局势能面搜索方法确定可抑制量子隧穿的最小稳定的Si/SiO2界面》(“Smallest stable Si/SiO2 interface that suppresses quantum tunneling from machine-learning-based global search”)为题在线发表于最新一期《物理评论快报》(Phys. Rev. Lett.)。

图1.(A)ML-Interface方法示意图;(B)预测的10个最稳定Si/SiO2界面结构。

应用新发展的ML-interface方法,研究筛选出了所有10个具有短周期性的Si/SiO2界面(图1B)。在这些界面中,除了已经在工业中使用的低密勒(Miller)指数界面Si(100)和Si(110)/SiO2被首次确定了原子结构,还发现了两个新的高密勒指数界面 Si(210)和Si(211)/SiO2。这两个高指数界面具有完美匹配的界面原子结构,优秀的热稳定性,和优秀的电子性质。相对于传统低密勒指数界面具有更高的载流子有效质量,在费米能级附近不具有任何界面态,理论表明可以显著降低载流子量子隧穿达四个数量级,同时界面尺寸也可以小至1纳米,有望实现更短的栅极长度。因此,理论预测新高Miller指数Si(210)和Si(211)/SiO2界面可能是突破Si基半导体性能瓶颈的关键,有望在鳍式场效应晶体管(FinFET)中得到应用。

最后,论文中预测的界面模型可以用来产生一系列关键物理参数,如有效质量、电导率和热导率,能加速芯片设计的宏观设备仿真(TCAD),同时,论文发展的界面搜索理论方法可以普遍应用于其他固体界面,辅助新型晶体管的设计和制造,如高电子迁移率晶体管(GaN)。

复旦大学化学系李晔飞教授和刘智攀教授为本论文的共同通讯作者,研究工作得到科技部重点研发计划、国家优秀青年科学基金、国家自然科学基金重点项目和面上项目,腾讯科学探索奖等项目的资助与支持。

全文链接:https://journals.aps.org/prl/accepted/c8072Y0fW9211975a64c3939ac594d5c80d1af8d7